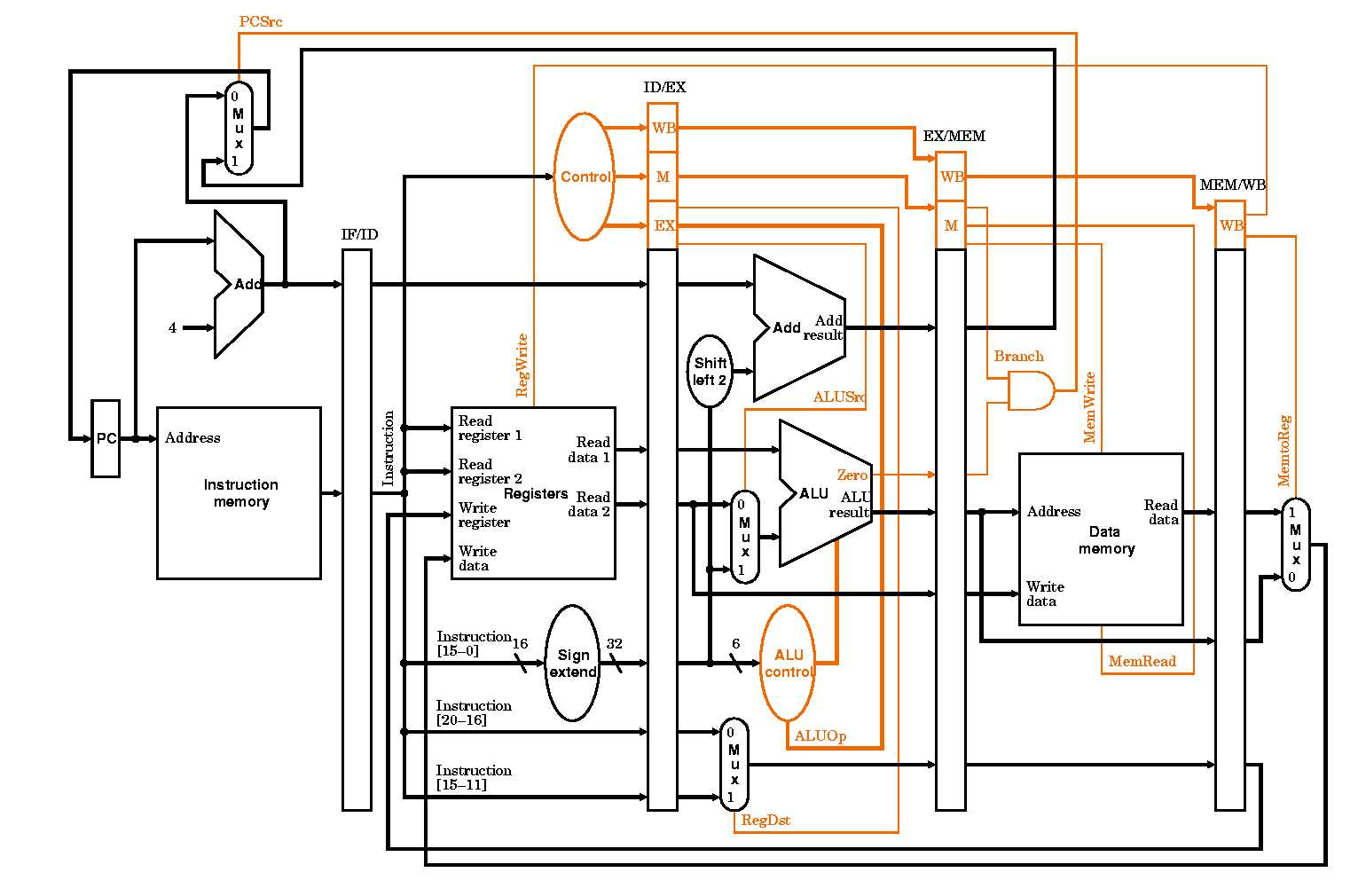

This project focuses on building a pipelined processor using Verilog and understanding how instructions move through different pipeline stages. The processor supports basic arithmetic, memory, and load operations while maintaining correct execution. A major focus of the project was identifying data hazards and testing how techniques like data forwarding help maintain correctness while improving execution speed. Through simulation and waveform analysis, this project helped me better understand how low level processor behavior works in practice.